$$f_A = \frac{1}{t_C} = \frac{1}{100 \cdot 10^{-9} seg} = 10^7 Hz$$

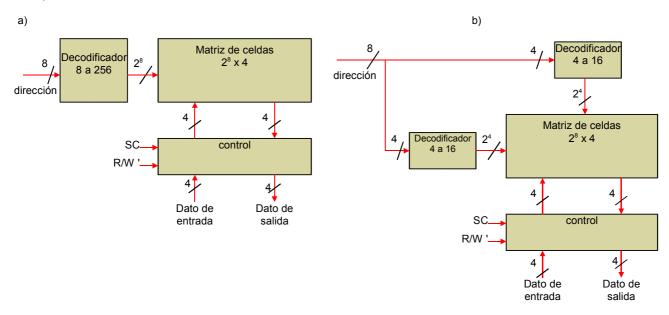

✓ Se pretende diseñar un módulo de memoria de 256 palabras de 4 bits. Calcule el número tamaño de los decodificadores con organización:

- a) 2D.

- b) 2½D.

Una de las situaciones más frecuentes con que se encuentra el ingeniero de sistemas digitales es esta: debe diseñar un sistema con unos requerimientos concretos; y los elementos con que cuenta no se ajustan a dichos requerimientos.

Si la funcionalidad de los elementos disponibles fuera superior a la requerida, no habría ninguna dificultad añadida en el diseño. El único inconveniente sería estar infrautilizando unos elementos para unas funciones menos complejas de lo que serían capaces de realizar. Si esta funcionalidad es menor, debe estudiar cómo acoplar varios elementos de un mismo tipo para obtener un elemento con mayores capacidades.

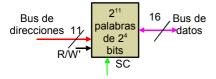

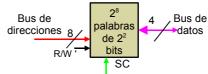

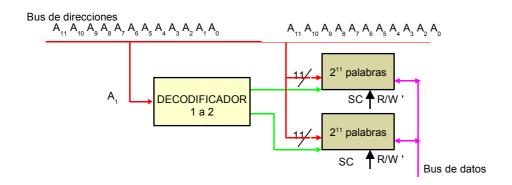

Se dispone de circuitos integrados de memoria RAM de 256x4 bits. ¿Cuántos son necesarios para proporcionar una capacidad de memoria de 2048 palabras de 16 bits?.

Estructura de la memoria principal requerida:

Estructura de los circuitos integrados disponibles:

Comenzaremos planteando estas dos ecuaciones:

|MP| = (N° de palabras en Memoria Principal ) = (N° de filas )\*  $\frac{N^{\circ} de palabras}{por circuito integrado}$

$$2^{11} = \left(\text{N}^{\text{o}} \text{ de filas }\right)^{*} \frac{2^{8} \text{ palabras}}{\text{por circuito integrado}} \Rightarrow \left(\text{N}^{\text{o}} \text{ de filas }\right) = \frac{2^{11}}{2^{8}} = 2^{3}$$

2)  $\mbox{Longitud de palabra en Memoria Principal} = \left( \mbox{N}^{o} \mbox{de columnas} \ \right)^{*} \frac{\mbox{Longitud de palabra}}{\mbox{en circuito integrado}}$

$$2^4 \text{bits} = \left( \text{N}^{\text{o}} \text{ de columnas } \right)^* \frac{2^2 \text{ bits}}{\text{en circuito } \text{ integrado}} \Rightarrow \left( \text{N}^{\text{o}} \text{ de columnas } \right) = \frac{2^4}{2^2} = 2^2$$

Por no recargar el diagrama, no se han detallado las conexiones de las patillas  $R/\overline{W}$ . La selección de función debe ser la misma para todos los CIs. Por este motivo, todas las patillas  $R/\overline{W}$  deben estar conectadas a una línea común. Esta línea es parte del Bus de Control.

✓ Sea un procesador que dispone de 12 líneas de direcciones A<sub>11</sub>-A<sub>0</sub>. Para la construcción de su unidad de memoria se dispone de módulos de 2K palabras, utilizándose la línea A1 para la selección de cada módulo (A0 es la línea menos significativa). ¿En qué módulos residirán las direcciones hexadecimales C89 y C8A?.

$$\begin{split} \left| \mathsf{MP} \right| &\equiv (\mathsf{N}^{\mathsf{o}} \, \mathsf{de} \, \mathsf{palabras} \, \mathsf{en} \, \mathsf{Memoria} \, \mathsf{Principal} \, ) = \left( \mathsf{N}^{\mathsf{o}} \, \mathsf{de} \, \mathsf{filas} \, \right)^{\star} \frac{\mathsf{N}^{\mathsf{o}} \, \mathsf{de} \, \mathsf{palabras}}{\mathsf{por} \, \mathsf{circuito} \, \mathsf{integrado}} \\ & 2^{10} = \left( \mathsf{N}^{\mathsf{o}} \, \mathsf{de} \, \mathsf{filas} \, \right)^{\star} \frac{2^{11} \, \mathsf{palabras}}{\mathsf{por} \, \mathsf{circuito} \, \mathsf{integrado}} \\ & \Rightarrow \left( \mathsf{N}^{\mathsf{o}} \, \mathsf{de} \, \mathsf{filas} \, \right) = \frac{2^{12}}{2^{11}} = 2^1 = 2 \end{split}$$

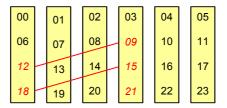

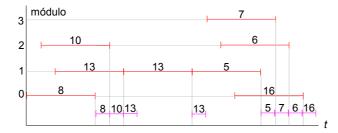

Las sucesivas direcciones se distribuyen entre ambos módulos de esta forma:

| sivas direcciones se distribuyen en | ntre ambos modulos de esta forma: |                             |  |  |  |  |  |  |  |  |  |  |

|-------------------------------------|-----------------------------------|-----------------------------|--|--|--|--|--|--|--|--|--|--|

| Dirección dentro del módulo         | mód                               | dulo                        |  |  |  |  |  |  |  |  |  |  |

|                                     | 0                                 | 1                           |  |  |  |  |  |  |  |  |  |  |

| 0                                   | 0000 0000 0000 (0)                | 0000 0000 0010 (2)          |  |  |  |  |  |  |  |  |  |  |

| 1                                   | 0000 0000 00 <mark>01 (1)</mark>  | 0000 0000 0011 (3)          |  |  |  |  |  |  |  |  |  |  |

| 2                                   | 0000 0000 0100 (4)                | 0000 0000 0110 (6)          |  |  |  |  |  |  |  |  |  |  |

| 3                                   | 0000 0000 0101 (5)                | 0000 0000 0111 (7)          |  |  |  |  |  |  |  |  |  |  |

| 4                                   | 0000 0000 1000 (8)                | 0000 0000 10 <b>1</b> 0 (A) |  |  |  |  |  |  |  |  |  |  |

| 5                                   | 0000 0000 1001 (9)                | 0000 0000 1011 (B)          |  |  |  |  |  |  |  |  |  |  |

|                                     |                                   |                             |  |  |  |  |  |  |  |  |  |  |

| 1100 1000 100 <sub>b</sub>          |                                   | 1100 1000 1010 (C8A)        |  |  |  |  |  |  |  |  |  |  |

| 1100 1000 101 <sub>b</sub>          | 1100 1000 10 <b>0</b> 1 (C89)     |                             |  |  |  |  |  |  |  |  |  |  |

|                                     |                                   |                             |  |  |  |  |  |  |  |  |  |  |

Por tanto la dirección C89 va al módulo 0 y la C8A va al módulo 1

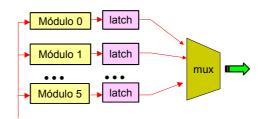

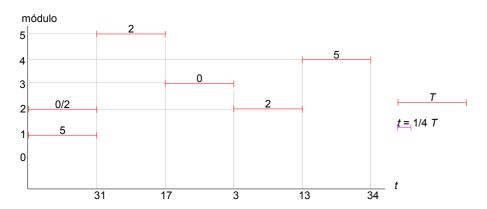

✓ Sea una memoria entrelazada de orden inferior con 6 módulos de 7 bytes cada uno y con *latches* en la salida. El procesador emite la siguiente secuencia de direcciones físicas (en base 10):

¿Cuántos ciclos de memoria son necesarios para completar dicha secuencia?.

| DF        | 31 | 17 | 3 | 13 | 34 |    |   |      |     |      |   |    |   |

|-----------|----|----|---|----|----|----|---|------|-----|------|---|----|---|

| Módulo    | 1  | 5  | 3 | 1  | 4  | 31 | 6 | 17 6 | 3 [ | 6 13 | 6 | 34 | 6 |

| Dirección | 5  | 2  | 0 | 2  | 5  | 1  | J | 5 2  | 3 ( | ) 1  | 2 | 4  | J |

Latches en la salida con acceso simultáneo a los módulos.

$$T = 5T + \frac{1}{4}T = \frac{21}{4}T = 5.25T$$

Son necesarios 5 ciclos de acceso a memoria, uno para cada módulo Cuando existen algunas direcciones iguales correspondientes a diferentes módulos, nos ahorramos algún ciclo. Existen dos direcciones iguales correspondientes a diferentes módulos: la 17 y la 13.

✓ Sea una memoria principal compuesta por 6 módulos de 4 palabras por módulo. El procesador emite la siguiente secuencia de direcciones físicas (todas son peticiones de lectura):

Calcule el número de palabras por ciclo que se pueden leer:

- a) Con entrelazamiento de orden superior.

- b) Con entrelazamiento de orden inferior.

#### a) Entrelazado de orden superior.

Distribuimos en cada módulo i;  $0 \le i \le M-1$ , todas las direcciones consecutivas entre  $i \cdot 2^{n-m}$  e  $(i+1) \cdot 2^{n-m}-1$  Los m bits más significativos de cada dirección indican el módulo y los restantes n-m determinan la posición.

Ciclo 1°. 9, 12

Ciclo 2°. 15, 18, 21

### b) Entrelazado de orden inferior.

Módulo de la forma  $0 \le i \le M-1$  y dirección  $K \cdot M+i$

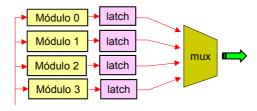

Si los cerrojos están a la salida, el proceso debe ser:

Ciclo 1°. 9 Ciclo 2°. 12, 15 Ciclo 3°. 18, 21

(iguales a las direcciones dentro de cada módulo)

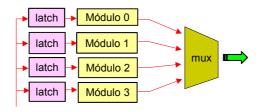

Si los cerrojos están a la entrada, el proceso también puede ser:

Ciclo 1°. 9, 12 Ciclo 2°. 15, 18 Ciclo 3°. 21 Sea un sistema con una memoria principal compuesta por cuatro módulos de ocho bytes cada uno, mediante un esquema de entrelazamiento de orden inferior. El procesador emite la siguiente secuencia de direcciones físicas:

Supongamos los dos siguientes casos:

- i. Latches en la salida.

- ii. Latches en la entrada.

Construya el diagrama de tiempos de acceso a los módulos, analizando en cuál de los dos casos es más rápida la respuesta de la memoria con dicha secuencia.

En el entrelazamiento de orden inferior los módulos consecutivos tienen direcciones de palabras consecutivas. Los m bits menos significativos se usan para seleccionar el módulo. El resto, la dirección.

| dire | cción | módulo |   |  |  |  |  |

|------|-------|--------|---|--|--|--|--|

| 8    | 010   | 00     | 0 |  |  |  |  |

| 10   | 010   | 10     | 2 |  |  |  |  |

| 13   | 011   | 01     | 1 |  |  |  |  |

| 13   | 011   | 01     | 1 |  |  |  |  |

| 5    | 001   | 01     | 1 |  |  |  |  |

| 7    | 001   | 11     | 3 |  |  |  |  |

| 6    | 001   | 10     | 2 |  |  |  |  |

| 16   | 100   | 00     | 0 |  |  |  |  |

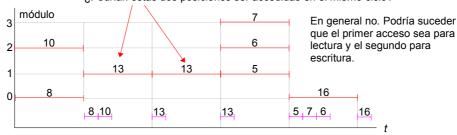

i. Con Latches en la salida.

¿Podrían estas dos posiciones ser accedidas en el mismo ciclo?

Tiempo =

$$T+1t=5T+\frac{1}{4}T=\frac{21}{4}T=5.2T$$

ii. Con Latches en la entrada.

Tiempo =

$$4T + 2t = 4T + \frac{2}{4}T = \frac{18}{4}T = 4.5T$$

La estrategia más rápida es la de latches en la entrada.

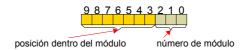

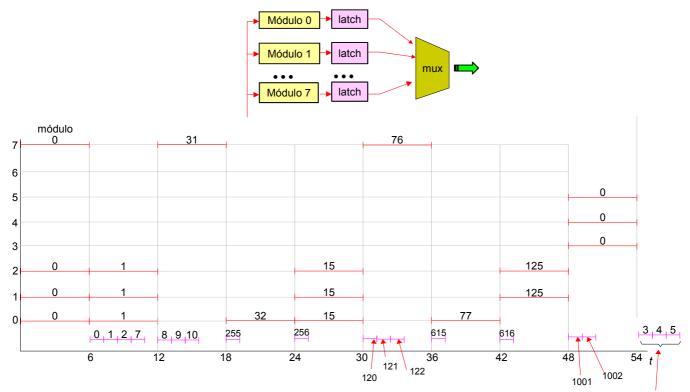

Sea un sistema con una memoria principal de 1 Kbyte dividida en ocho módulos iguales mediante un esquema de entrelazamiento de orden inferior.

## Suponga que:

- La salida de un dato del sistema de memoria consume 1 unidad temporal.

- ✔ El acceso a un módulo consume 6 unidades temporales.

# El procesador emite la siguiente secuencia de direcciones físicas:

0, 1, 2, 7, 8, 9, 10, 255, 256, 120, 121, 122, 615, 616, 1001, 1002, 3, 4 y 5.

Construya el diagrama de tiempos de acceso a los módulos en los dos siguientes casos:

- i. Latches en la salida.

- ii. Latches en la entrada

Direcciones en cada módulo:  $\frac{2^{10}}{3^3} = 2^7$  , es decir, 7 bits para la posición dentro del módulo.

| Dirección física  | Dirección                                | Módulo                   | Dirección      | Módulo           |

|-------------------|------------------------------------------|--------------------------|----------------|------------------|

| 0<br>1<br>2<br>7  | 0000000<br>0000000<br>0000000<br>0000000 | 000<br>001<br>010<br>111 | 0<br>0<br>0    | 0<br>1<br>2<br>7 |

| 8<br>9<br>10      | 0000001<br>0000001<br>0000001            | 000<br>001<br>010        | 1<br>1<br>1    | 0<br>1<br>2      |

| 255               | 0011111                                  | 111                      | 31             | 7                |

| 256               | 0100000                                  | 000                      | 32             | 0                |

| 120<br>121<br>122 | 0001111<br>0001111<br>0001111            | 000<br>010<br>010        | 15<br>15<br>15 | 0<br>1<br>2      |

| 615               | 1001100                                  | 111                      | 76             | 7                |

| 616               | 1001101                                  | 000                      | 77             | 0                |

| 1001<br>1002      | 1111101<br>1111101                       | 001<br>010               | 125<br>125     | 1<br>2           |

| 3<br>4<br>5       | 0000000<br>0000000<br>0000000            | 011<br>100<br>101        | 0<br>0<br>0    | 3<br>4<br>5      |

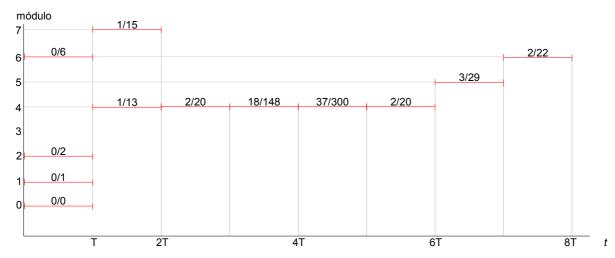

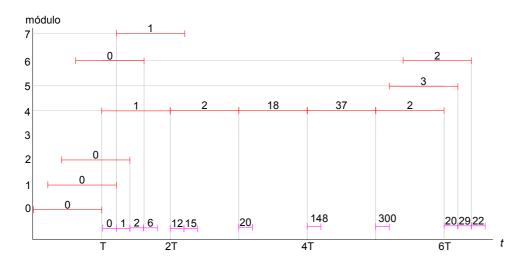

i. Latches en la salida. Gestión a la entrada: en la entrada se selecciona una dirección de entre los diferentes módulos.

Uno por cada módulo leído en la anterior etapa

El acceso a los módulos es simultáneo.

Tiempo = 9 T + 3 t = 9 · 6 u + 3 u = 57 unidades de tiempo.

## ii. Latches en la entrada.

El acceso a los módulos es retardado.

Tiempo = 6 T = 6 · 6 u = 367 unidades de tiempo.

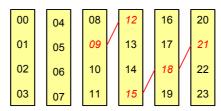

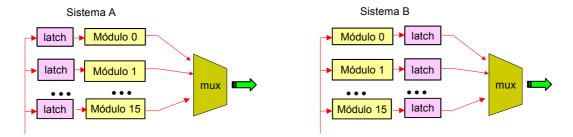

Considere dos sistemas A y B cuya memoria principal está dividida en 16 módulos idénticos y entrelazados según el esquema de orden inferior. Cada sistema posee 16 cerrojos. En el sistema A están colocados en los buses de direcciones de los módulos. En el sistema B están colocados en los buses de datos (uno en cada bus). Ponga ejemplos de tres secuencias de peticiones de acceso a memoria de tal manera que el número de palabras accedidas por ciclo de memoria sea:

- a) Mayor en A que en B.

- b) Igual en A que en B.

- c) Menor en A que en B.

El acceso a varias palabras en cada ciclo está permitido si:

- Sistema A: Las palabras están en módulos diferentes, en cualquier posición.

- Sistema B: Las palabras están en módulos diferentes, en la misma posición.

- a) A>B: 0, 3, 6, 9, 12, 15, 18, 21, ...

| 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 10 | 11 | 12 | 13 | 14 | 15 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 |

| 48 | 49 | 50 | 51 | 52 | 53 | 54 | 55 | 56 | 57 | 58 | 59 | 60 | 61 | 62 | 63 |

| 64 | 65 | 66 | 67 | 68 | 69 | 70 | 71 | 72 | 73 | 74 | 75 | 76 | 77 | 78 | 79 |

b) A = B: 0, 1, 2, 3, 4, 5, 6, 7, ... o también, por ejemplo: 0, 16, 32, 48, 64, ...

| 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 80 | 09 | 10 | 11 | 12 | 13 | 14 | 15 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 |

| 48 | 49 | 50 | 51 | 52 | 53 | 54 | 55 | 56 | 57 | 58 | 59 | 60 | 61 | 62 | 63 |

| 64 | 65 | 66 | 67 | 68 | 69 | 70 | 71 | 72 | 73 | 74 | 75 | 76 | 77 | 78 | 79 |

c) A < B: No es posible.

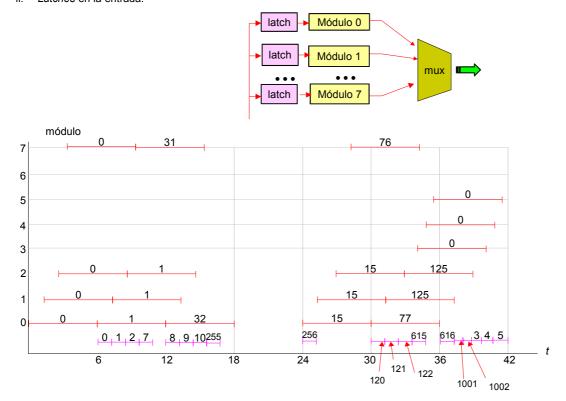

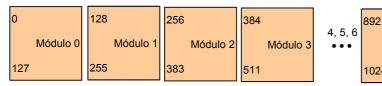

Sea un sistema con una memoria principal de 1 Kbyte compuesta por ocho módulosiguales. El procesador emite la siguiente secuencia de direcciones físicas:

Trace el diagrama de tiempos de acceso a los módulos en cada uno de los tres casos siguientes:

- Esquema de entrelazamiento de orden superior.

- Esquema de entrelazamiento de orden inferior con latches en la salida. ii.

- Esquema de entrelazamiento de orden inferior con latches en la entrada. iii.

i.

$$\frac{2^{10} \, bytes}{2^3 \, m\'odulos} = 2^7 \frac{bytes}{m\'odulo} \implies 7 \, bits \, por \, palabra$$

| DF        |                  | 0 | 1 | 2 | 6 | 12 | 15 | 20 | 148 | 300 | 20 | 29 | 22 |

|-----------|------------------|---|---|---|---|----|----|----|-----|-----|----|----|----|

| Módulo=   | $\frac{DF}{2^7}$ | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 1   | 2   | 0  | 0  | 0  |

| Dirección |                  | 0 | 1 | 2 | 6 | 12 | 15 | 20 | 20  | 44  | 20 | 25 | 22 |

Módulo 7

1024

Se da el caso de que hay diferentes módulos con iguales direcciones. Tiempo = 7 ciclos de reloj.

10 direcciones dentro del mismo módulo ⇒ 10 ciclos de memoria.

Entrelazamiento de orden inferior con latches en la salida. Existe el riesgo de un conflicto de memoria por intentar acceder a módulos iguales.

| DF        |                  | 0 | 1 | 2 | 6 | 12 | 15 | 20 | 148 | 300 | 20 | 29 | 22 |

|-----------|------------------|---|---|---|---|----|----|----|-----|-----|----|----|----|

| Módulo=   | $\frac{DF}{2^3}$ | 0 | 0 | 0 | 0 | 1  | 1  | 2  | 18  | 37  | 2  | 3  | 2  |

| Dirección |                  | 0 | 1 | 2 | 6 | 4  | 7  | 4  | 4   | 4   | 4  | 5  | 6  |

Se da el caso de que hay módulos distintos con las mismas direcciones.

Tiempo=8T. 8 ciclos de memoria.

## iii. Entrelazamiento de orden inferior con latches en la entrada.

Siempre direcciones diferentes con módulos diferentes. Puede ocurrir un conflicto de memoria por intentar acceder a módulos iguales.

| DF        | 0 | 1 | 2 | 6 | 12 | 15 | 20 | 148 | 300 | 20 | 29 | 22 |

|-----------|---|---|---|---|----|----|----|-----|-----|----|----|----|

| Dirección | 0 | 0 | 0 | 0 | 1  | 1  | 2  | 18  | 37  | 2  | 3  | 2  |

| Módulo    | 0 | 1 | 2 | 6 | 4  | 7  | 4  | 4   | 4   | 4  | 5  | 6  |

Tiempo =  $6T + 3t = 6T + \frac{3}{4}T = \frac{27}{4}T = 6.75T$

|                  | Orden inferior |      |        |  |  |  |  |  |  |  |

|------------------|----------------|------|--------|--|--|--|--|--|--|--|

| Dirección física | Direc          | ción | Módulo |  |  |  |  |  |  |  |

| 0                | 000            | 0000 | 000    |  |  |  |  |  |  |  |

| 1                | 000            | 0000 | 001    |  |  |  |  |  |  |  |

| 2                | 000            | 0000 | 010    |  |  |  |  |  |  |  |

| 6                | 000            | 0000 | 110    |  |  |  |  |  |  |  |

| 12               | 000            | 0001 | 100    |  |  |  |  |  |  |  |

| 15               | 000            | 0001 | 111    |  |  |  |  |  |  |  |

| 20               | 000            | 0010 | 100    |  |  |  |  |  |  |  |

| 148              | 001            | 0010 | 100    |  |  |  |  |  |  |  |

| 300              | 010            | 0101 | 100    |  |  |  |  |  |  |  |

| 20               | 000            | 0010 | 100    |  |  |  |  |  |  |  |

| 29               | 000            | 0011 | 101    |  |  |  |  |  |  |  |

| 22               | 000            | 0010 | 110    |  |  |  |  |  |  |  |

|                  | Módulo         | Dire | ección |  |  |  |  |  |  |  |

|                  | Orden superior |      |        |  |  |  |  |  |  |  |