# TEMA VI

DISEÑO DEL PROCESADOR

#### Diseño del procesador

- 6.1 Repertorio de instrucciones

- 6.1.1 Procesadores de tres direcciones

- 6.1.2 Procesadores de dos direcciones

- 6.1.3 Procesadores de una dirección (procesadores con acumulador)

- 6.1.4 Procesadores de cero direcciones (procesadores con pila)

- 6.1.5 Procesadores sin ALU

- 6.1.6 Análisis de las diferentes arquitecturas de procesadores

- 6.1.7 Procesadores con banco de registros

- 6.1.8 Arquitectura de carga/almacenamiento: Procesadores RISC

- 6.2 Modos de direccionamiento

- 6.3 Ciclo de ejecución de una instrucción

- 6.3.1 Fase de búsqueda de la instrucción

- 6.3.2 Fase de decodificación de la instrucción

- 6.3.3 Fase de búsqueda de los operandos

- 6.3.4 Fase de ejecución de la instrucción

- 6.3.5 Transferencia a un subprograma

- 6.3.6 Ciclo de interrupción

- 6.4 Fases en el diseño del procesador

- 6.5 Diseño de un procesador elemental

- 6.5.1 Especificación del procesador SIMPLE1

- 6.5.2 Repertorio de instrucciones

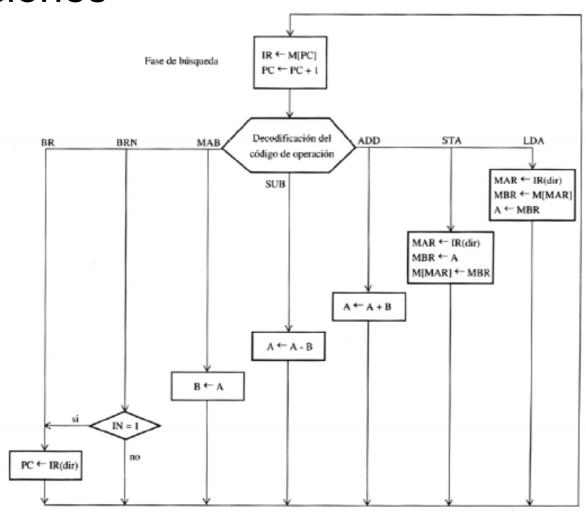

- 6.5.3 Diagrama de flujo del repertorio de instrucciones

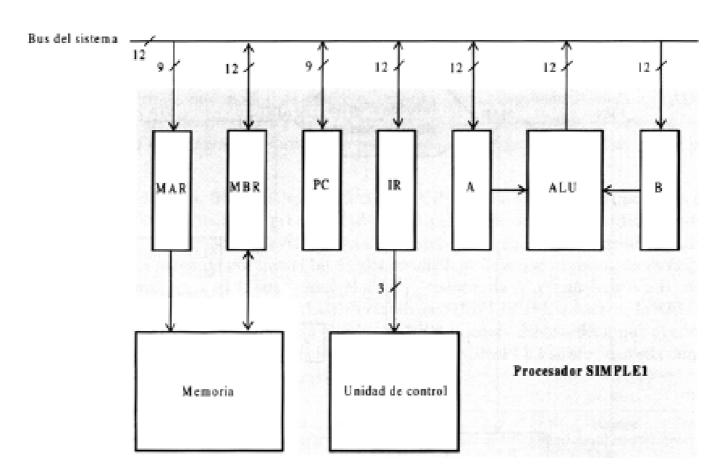

- 6.5.4 Asignación de recursos a la unidad de procesamiento o ruta de datos

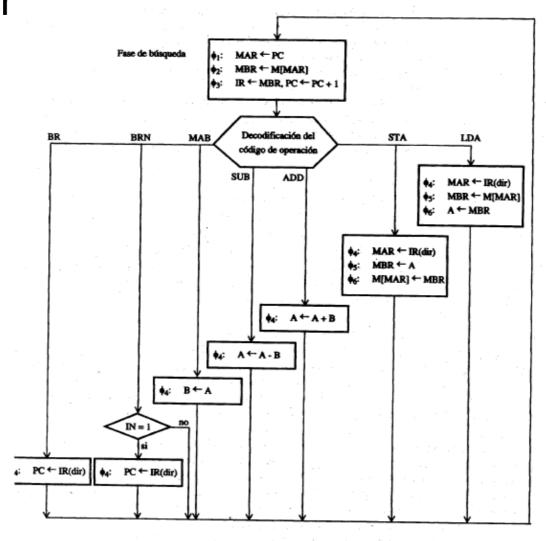

- 6.5.5 Obtención del diagrama ASM del procesador

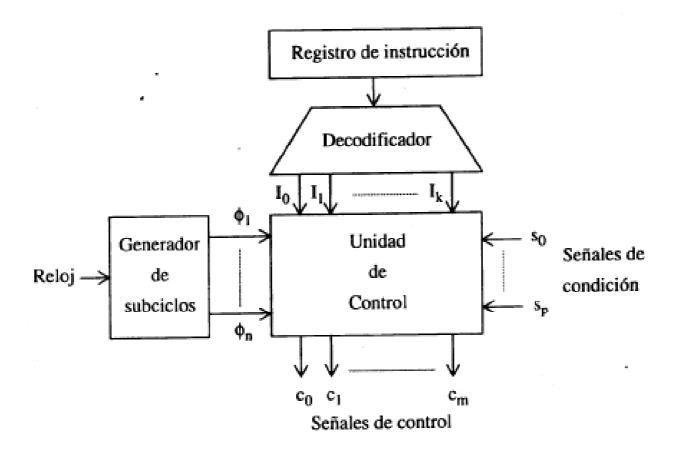

- 6.5.6 Diseño de la unidad de control

- 6.5.7 Diseño de la unidad de procesamiento o ruta de datos

- 6.2 Modos de direccionamiento

- El modo de direccionamiento determina la forma que se interpreta el contenido del campo de dirección de una instrucción

- El modo de direccionamiento permite calcular de forma no ambigua la dirección real donde se encuentra los operandos

- Las ventajas:

- Reducción del tamaño de las instrucciones

- Aumento de la flexibilidad de la programación

- Modos de direccionamiento

- Implícito

- Inmediato

- Directo

- Relativo

- Indirecto

- □ Indexado

# DISEÑO DEL PROCESADOR

- Partes de un sistema digital

- □ Unidad de procesamiento:

- Se almacenan y transforman los datos

- ☐ Unidad de control:

- Genera las secuencias se señales de control de acuerdo al algoritmo de transferencia de registros.

- Tipos de microoperaciones

- □ De transferencia

- □ De proceso

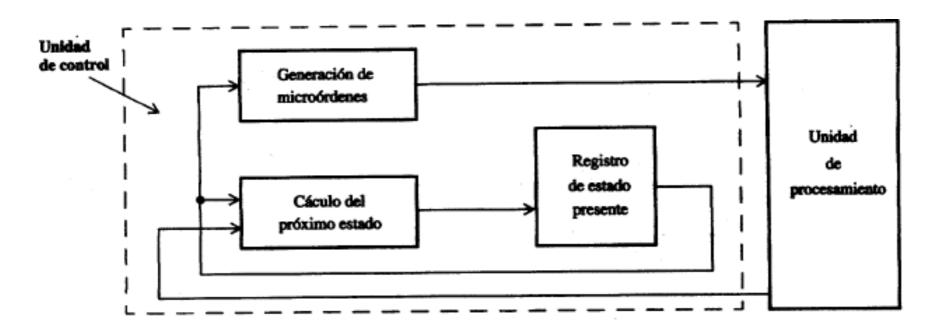

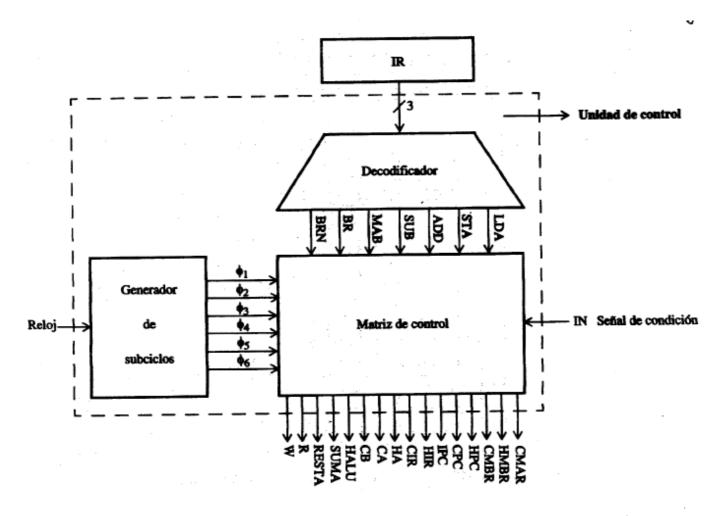

Figura 6.2: Estructura de una unidad de control con lógica cableada

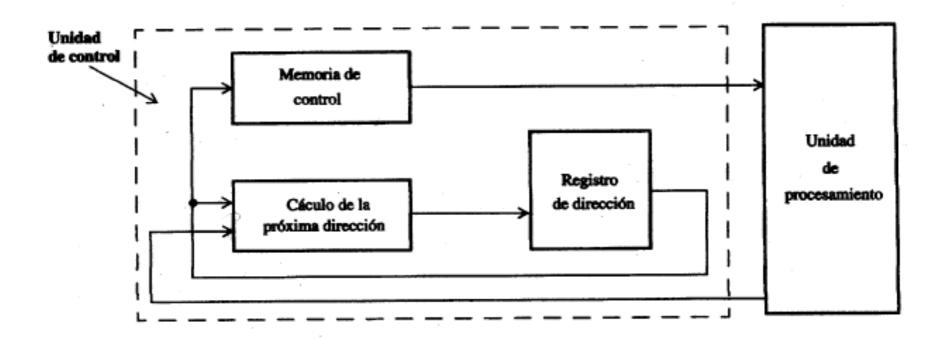

Figura 6.3: Estructura de una unidad de control microprogramada

## 6.1 Repertorio de instrucciones

- Cada CPU tiene su propio y especifico formato de instrucciones

- Una instrucción una cadena de bits que se agrupan en campos con tamaños diferentes

- Tipos de instrucciones

- □ De transferencia de datos

- □ Aritméticas, lógicas y de comparación

- □ De desplazamiento

- □ De Transferencia de control

- De gobierno

- Tipos de procesadores según el número de direcciones

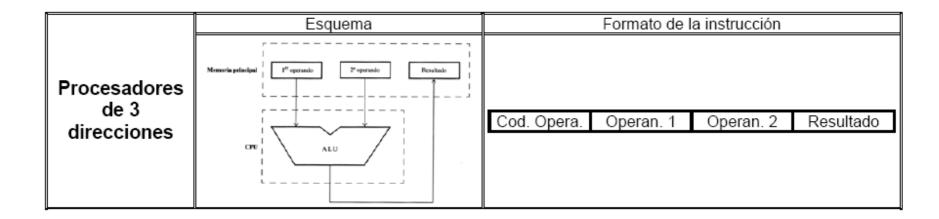

- □ 3 direcciones

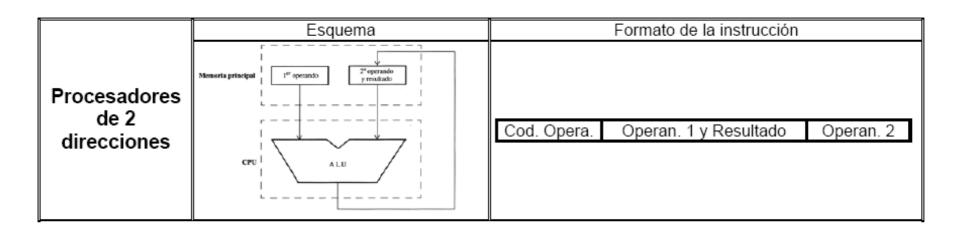

- 2 direcciones

- 1 dirección

- □ 0 direcciones

# r

#### 6.1.1 Procesadores de tres direcciones

- Requiere un número elevado de bits para codificarla

- Programas cortos

# ×

#### 6.1.2 Procesadores de dos direcciones

- Mayor longitud del programa

- Menor número de acceso a memoria que necesitan las instrucciones

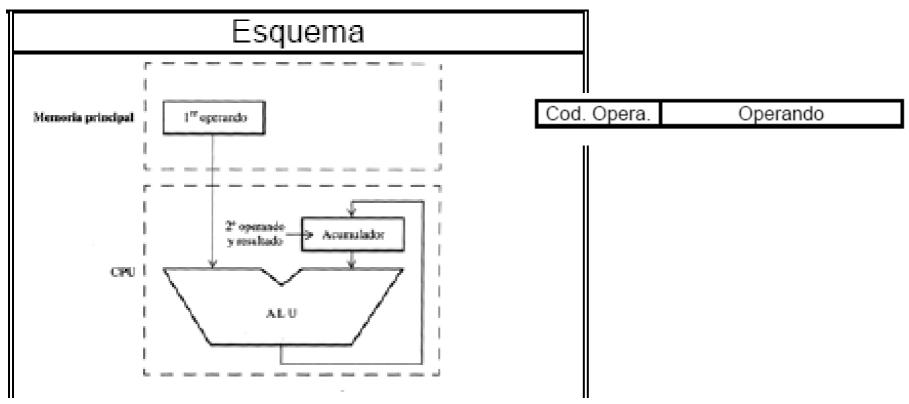

# 6.1.3 Procesadores de una dirección (procesadores con acumulador)

El procesador dedica un registro como operando destino

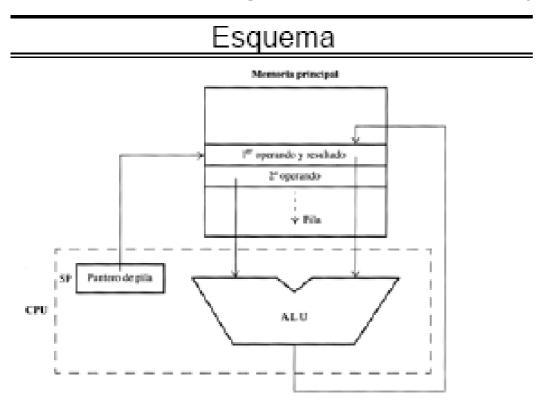

# 6.1.4 Procesadores de cero direcciones (procesadores con pila)

Primer, segundo operando y resultado en la pila

Código Operación

Flujo de datos en un procesador de pila en las instrucciones con referencia a memoria

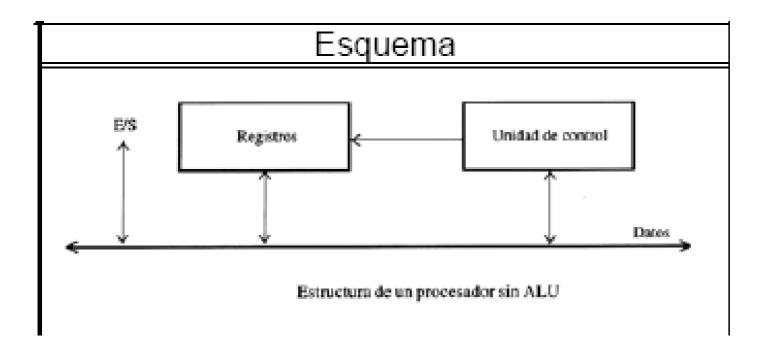

### 6.1.5 Procesadores sin ALU

Operaciones de transferencia

- 6.1.6 Análisis de las diferentes arquitecturas de procesadores

- Se han analizados instrucciones ternarias:

- □ Dos operandos y un resultado

- El número de instrucciones aumenta conforme disminuye en número de operandos explícitos en cada instrucción

# и.

### 6.1.7 Procesadores con banco de registros

La idea del procesador con acumulador puede generalizarse incrementando el número de registros (banco de registros)

#### Ventajas:

- Al almacenar los resultados intermedios en registros en vez de en memoria principal aumenta la velocidad

- □ Menor tamaño de las instrucciones.

- En vez de una dirección de memoria, en la instrucción aparece el número de registro (se necesitan menos bits para direccionarlos)

# 6.1.8 Arquitectura de carga/almacenamiento: Procesadores RISC

- RISC (Reduce Instruction Set Computer)

- □ Arquitectura Carga/almacenamiento

- Se accede a memoria solo para extraer datos o poner resultados

- El resto de las operaciones se realizan en los registros

- Instrucciones sencillas (operaciones elementales)

- □ Formato de instrucciones regular (misma longitud)

- Unidad de control cableada y ciclo por instrucción suele ser uno

- □ Modo de direccionamientos limitados

- CISC (Complex Instruction Set Computer)

- 6.3 Ciclo de ejecución de una instrucción

- 6.3.1 Fase de búsqueda de la instrucción

- 6.3.2 Fase de decodificación de la instrucción

- 6.3.3 Fase de búsqueda de los operandos

- 6.3.4 Fase de ejecución de la instrucción

- 6.3.5 Transferencia a un subprograma

- 6.3.6 Ciclo de interrupción

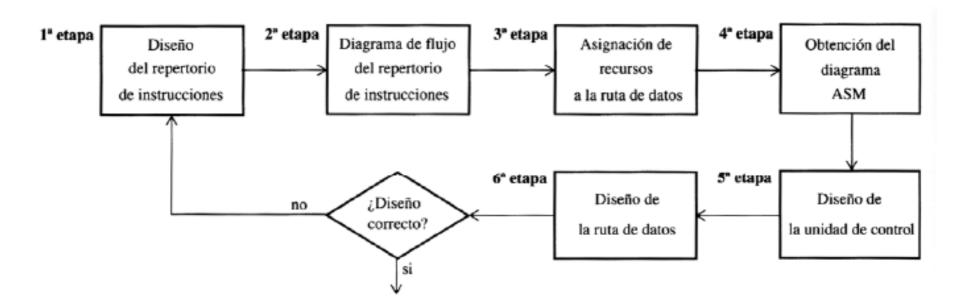

# 6.4 Fases en el diseño del procesador

Etapas en el diseño del procesador

# 6.5 Diseño de un procesador elemental

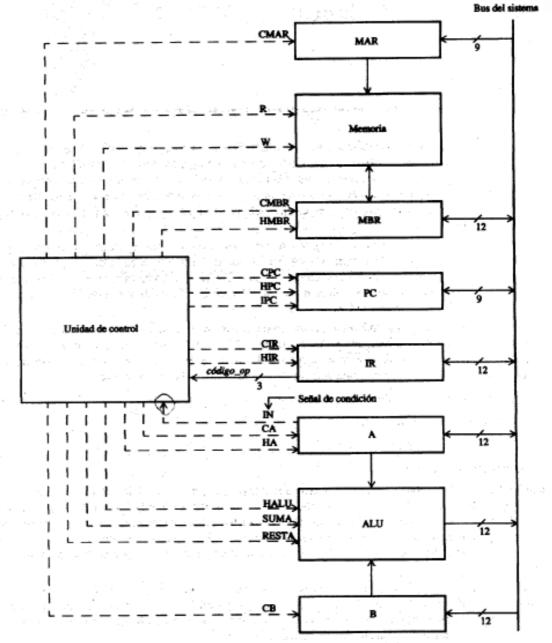

- 6.5.1 Especificación del procesador SIMPLE1

- □ SIMPLE1 ordenador elemental académico

- □ Registros

- Registro contador de programa (PC): Como la capacidad del operando

→ 9 bits

- Reg. Instrucciones (IR): Anchura del formato de la instrucción → 12 bits

- Reg. Direcc. Mem. (MAR): Capacidad de direccionamiento → 9 bits

- Reg. Datos de memoria (MBR): Anchura del formato de la instruc. → 12 bits

- Registros de trabajo A , B: Como la capacidad del operando → 9 bits

- ALU: Suma / resta

- □ Formato de instrucción:

| 1 | 1            | 10 | တ | 8 | 7 | 6 | 5 | 4     | 3  | 2 | 1 | 0 |

|---|--------------|----|---|---|---|---|---|-------|----|---|---|---|

| С | Cod. Operac. |    |   |   |   |   | O | beran | do |   |   |   |

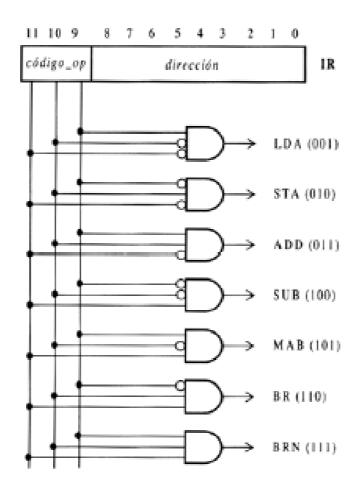

# 6.5.2 Repertorio de instrucciones

| Nemotécnico | Código binario | Instrucción                         | Acción                               |

|-------------|----------------|-------------------------------------|--------------------------------------|

| LDA x       | LDA = 001      | Carga directa                       | $A \leftarrow M[x]$                  |

| STA x       | STA = 010      | Almacenamiento directo              | $M[x] \leftarrow A$                  |

| ADD         | ADD = 011      | Suma B a A                          | $A \leftarrow A + B$                 |

| SUB         | SUB = 100      | Resta B de A                        | A ← A - B                            |

| MAB         | MAB = 101      | Mueve A a B                         | B ← A                                |

| BR x        | BR = 110       | Salto incondicional a x             | PC ← x                               |

| BRN x       | BRN = 111      | Salto a x si indicador negativo a 1 | $PC \leftarrow x \text{ si } IN = 1$ |

Repertorio de instrucciones de SIMPLE1

# 6.5.3 Diagrama de flujo del repertorio de instrucciones

# 6.5.4 Asignación de recursos a la unidad de procesamiento o ruta de datos

NO SE HAN INCLUIDO LAS SEÑALES DE CONTROL Y CONDICIÓN

6.5.5 Obtención del diagrama ASM del procesador

Figura 6.43: Diagrama ASM del procesador SIMPLE1

## 6.5.6 Diseño de la unidad de control

Entradas IR, Señales de condición y Reloj

IR: Necesita un decodificador

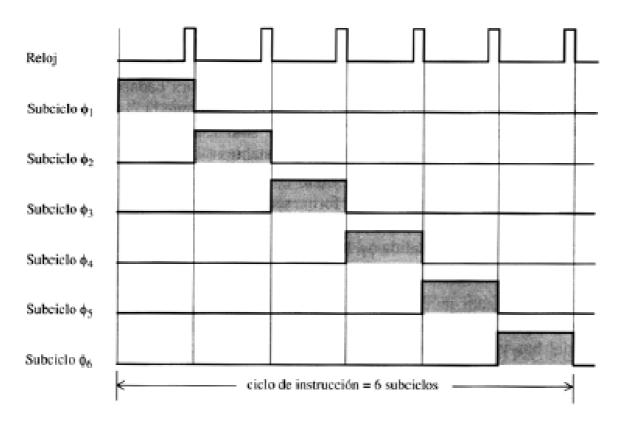

Reloj: Dividir el ciclo de una instrucción en subciclos

### Señales de control del SIMPLE1

| Señal de<br>control | Microorden controlada                                          |  |  |  |  |  |  |  |  |

|---------------------|----------------------------------------------------------------|--|--|--|--|--|--|--|--|

| R                   | Leer de la memoria (MBR ← M[MAR])                              |  |  |  |  |  |  |  |  |

| w                   | Escribir en la memoria (M[MAR] ← MBR)                          |  |  |  |  |  |  |  |  |

| CMAR                | Cargar el contenido del bus en MAR (MAR ← Bus)                 |  |  |  |  |  |  |  |  |

| HMBR                | Habilitar el registro MBR (Bus ← MBR)                          |  |  |  |  |  |  |  |  |

| CMBR                | Cargar el contenido del bus en MBR (MBR ← Bus)                 |  |  |  |  |  |  |  |  |

| HPC                 | Habilitar el registro PC (Bus ← PC)                            |  |  |  |  |  |  |  |  |

| CPC                 | Cargar el contenido del bus en PC (PC ← Bus)                   |  |  |  |  |  |  |  |  |

| IPC                 | Incrementar el contenido de PC (PC ← PC + 1)                   |  |  |  |  |  |  |  |  |

| HIR                 | Habilitar el registro IR (Bus ← IR)                            |  |  |  |  |  |  |  |  |

| CIR                 | Cargar el contenido del bus en IR (IR ← Bus)                   |  |  |  |  |  |  |  |  |

| НА                  | Habilitar el registro A (Bus $\leftarrow$ A)                   |  |  |  |  |  |  |  |  |

| CA                  | Cargar el contenido del bus en A (A ← Bus)                     |  |  |  |  |  |  |  |  |

| СВ                  | Cargar el contenido del bus en B (B ← Bus)                     |  |  |  |  |  |  |  |  |

| HALU                | Habilitar la unidad aritmético-lógica                          |  |  |  |  |  |  |  |  |

| SUMA                | Seleccionar la función de suma en la unidad aritmético-lógica  |  |  |  |  |  |  |  |  |

| RESTA               | Seleccionar la función de resta en la unidad aritmético-lógica |  |  |  |  |  |  |  |  |

|   | Habilitar salida de registro a bus |

|---|------------------------------------|

| C | Cargar registro desde bus          |

#### Unidad de Control del SIMPLE1

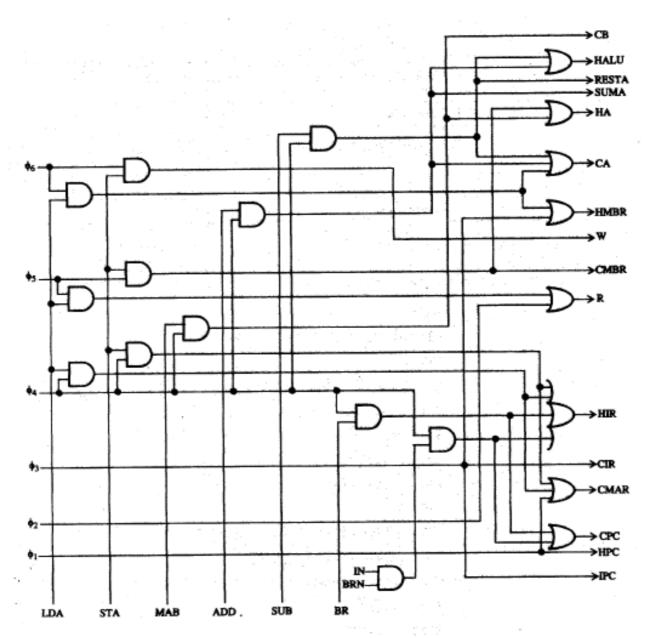

Figura 6.45: Unidad de control del procesador SIMPLE1 con decodificación de sus entradas

#### Decodificador del SIMPLE1

Decodificador de instrucciones del procesador SIMPLE1

### División del ciclo de instrucción

División del ciclo de instrucción del procesador SIMPLE1 en 6 subciclos

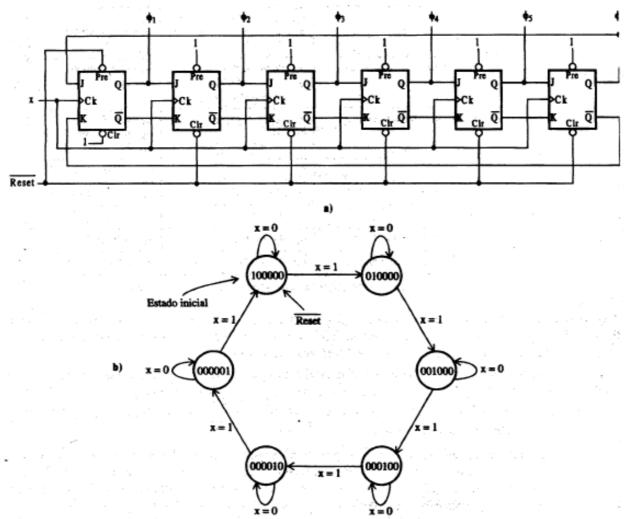

### Contador en anillo en módulo 6

Figura 6.48: Contador en anillo módulo-6: a) Circuito lógico; b) Diagrama de estado

# Señales de control

icuvai para caua una un morte per-----

| [        | Acción                              | Microoperaciones                                                                                                                    | Señales de control                                                                                                                                |

|----------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Búsqueda | Fase de búsqueda de la instrucción  | <ul> <li>\$\phi_1\$: MAR ← PC;</li> <li>\$\phi_2\$: MBR ← M[MAR];</li> <li>\$\phi_3\$: IR ← MBR,</li> <li>\$PC ← PC + 1;</li> </ul> | <ul> <li>♦₁: HPC, CMAR</li> <li>♦₂: R</li> <li>♦₃: HMBR, CIR, IPC</li> </ul>                                                                      |

| LDA x    | Carga directa                       | <ul> <li>\$\psi_4\$: MAR ← IR(dir);</li> <li>\$\psi_5\$: MBR ← M[MAR];</li> <li>\$\psi_6\$: A ← MBR;</li> </ul>                     | <ul> <li>♦4: HIR, CMAR</li> <li>♦5: R</li> <li>♦6: HMBR, CA</li> </ul>                                                                            |

| STA dir  | Almacenamiento directo              | <ul> <li>\$\psi_4\$: MAR ← IR(dir);</li> <li>\$\psi_5\$: MBR ← A;</li> <li>\$\psi_6\$: M[MAR] ← MBR;</li> </ul>                     | <ul> <li>         ∮<sub>4</sub>: HIR, CMAR     </li> <li>         ∮<sub>5</sub>: HA, CMBR     </li> <li>         ∮<sub>6</sub>: W     </li> </ul> |

| ADD      | Suma B a A                          | <b>♦</b> 4: A←A+B;                                                                                                                  | ♦4: SUMA, HALU, CA                                                                                                                                |

| SUB      | Resta B de A                        | <b>φ</b> <sub>4</sub> : A ← A - B;                                                                                                  | ♦4: RESTA, HALU, CA                                                                                                                               |

| MAB      | Mueve A a B                         | <b>♦</b> 4: B←A;                                                                                                                    | <b>♦</b> 4: НА, СВ                                                                                                                                |

| BR x     | Salto incondicional a x             | \$\ddag{4}: PC ← IR(dir);  \$\dag{dir}\$;                                                                                           | ♦4: HIR, CPC                                                                                                                                      |

| BRN x    | Salto a x si indicador negativo a 1 | $\phi_4$ : PC $\leftarrow$ IR(dir) (si IN = 1);                                                                                     | <b>♦</b> 4: si IN = 1: HIR, CPC                                                                                                                   |

Tabla 6.8: Señales de control que hay que activar en cada microoperación

# Matriz lógica

|          | IPC        | CPC .             | HPC         | CMAR       | R          | w          | CMBR       | HMBR        | CIR        | HIR        | CA          | HA         | SUMA        | RESTA      | HALU        | СВ          |

|----------|------------|-------------------|-------------|------------|------------|------------|------------|-------------|------------|------------|-------------|------------|-------------|------------|-------------|-------------|

| Búsqueda | <b>♦</b> 3 |                   | <b>\$</b> 1 | <b>•</b> 1 | <b>•</b> 2 |            |            | <b>\$</b> 3 | <b>♦</b> 3 |            |             |            |             |            |             |             |

| LDA      |            |                   |             | <b>♦</b> 4 | <b>♦</b> 5 |            |            | <b>♦</b> 6  |            | <b>♦</b> 4 | <b>♦</b> 6  |            |             |            |             |             |

| STA      |            |                   |             | <b>♦</b> 4 |            | <b>♦</b> 6 | <b>♦</b> 5 | 4           |            | <b>∳</b> 4 |             | <b>♦</b> 5 |             |            |             |             |

| ADD      |            |                   |             |            |            |            | -          |             |            |            | <b>\$</b> 4 |            | <b>\$</b> 4 |            | <b>♦</b> 4  | L           |

| SUB      |            |                   |             |            |            |            |            |             |            |            | <b>\$</b> 4 |            |             | <b>\$4</b> | <b>\$</b> 4 |             |

| MAB      |            |                   |             |            |            |            |            |             |            |            |             | 44         |             |            |             | <b>\$</b> 4 |

| BR       |            | +4                |             |            |            |            |            |             |            | . \$4      |             |            |             |            |             |             |

| BRN      |            | φ <sub>4</sub> IN |             |            |            |            |            |             |            | ♦4 IN      |             |            |             |            |             |             |

Tabla 6.9: Matriz de instantes de activación de las señales de control para cada instrucción de SIMPLE1

$$IPC = \phi_3$$

$$CPC = \phi_4 BR + \phi_4 IN BRN$$

$$HPC = \phi_1$$

$$CMAR = \phi_1 + \phi_4 LDA + \phi_4 STA$$

$$R = \phi_2 + \phi_5 LDA$$

$$W = \phi_6 STA$$

$$CMBR = \phi_5 STA$$

$$HMBR = \phi_3 + \phi_6 LDA$$

$$CIR = \phi_3$$

$$HIR = \phi_4 LDA + \phi_4 STA + \phi_4 BR + \phi_4 IN BRN$$

$$CA = \phi_6 LDA + \phi_4 ADD + \phi_4 SUB$$

$$HA = \phi_5 STA + \phi_4 MAB$$

$$SUMA = \phi_4 ADD$$

RESTA =

$$\phi_4$$

SUB

$$HALU = \phi_4 ADD + \phi_4 SUB$$

$$CB = \phi_4 MAB$$

Fleura 6.49: Matriz de control del procesador SIMPLE1

6.5.7 Diseño de la unidad de procesamiento o ruta de datos

Figura 6.50: Procesador SIMPLE1 y su conexión con la memoria

- ×

- En un procesador con instrucciones de cero direcciones (procesador con pila), indique si las secuencias de instrucciones propuestas calculan la expresión X=Y²(X+Z)

- □ I. Push[X]; Push[Z]; Add; Push[Y]; Push[Y]; Mult; Mult; Pop[X]

- □ II. Push[Y]; Push[X]; Push[Z]; Add; Mult; Mult; Pop[X]

- A) I:sí, II:sí

- B) I:sí, II:no

- C) I:no, II:sí

- D) I:no, II:no

| <ul> <li>En un procesador con instrucciones de cero direcciones, indicar cual accesos a memoria se necesitan para completar la secuencia Y = (X+Y)+Z.</li> <li>A) 10.</li> <li>B) 6.</li> <li>C) 12.</li> <li>D) Ninguna de las anteriores.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ntos    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| <ul> <li>Solución</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |

| <ul> <li>[Ver el problema 6-4 y el apartado 6.1.4 del texto de teoría.]</li> <li>En el caso de un procesador de cero direcciones el cálculo de la expresión dada se puede realizar mediante el conjunto de 6 instrucciones siguientes: Push[X]; Push[Y]; Add; Push[Z]; Add; Pop[Y]</li> <li>Serán necesarios 6 accesos a memoria para leer el código de operación de cada instrucción;</li> <li>además en el caso de las instrucciones Push y Pop se necesita acceso adicional a memoria para acceder a los operandos, ya que las operaciones aritméticas se realizan con operandos que se encuentran ya en la pila.</li> <li>En total son 6 instrucciones, tres de las cuales son Push y una P 6+3+1 = 10 accesos</li> <li>Respuesta: A</li> </ul> | un<br>e |

#### Empleando un procesador de una dirección (procesador con acumulador) con un banco de registro Ri, indicar qué operación calcula la secuencia de instrucciones:

- □ Load X; Add Y; Add Z; Mult X, Store R1, Mult R1, Div X, Store X.

- A)  $X = ((X+Y+Z)^2)X^2$

- B)  $X = ((X+Y+Z)^2)X$

- C)  $X = (X+Y+Z)^2$

- D) Ninguna de las anteriores

- El resultado de la ejecución de la secuencia de instrucciones propuesta es:

- $(((X + Y + Z)X)^2)/X = ((X + Y + Z)^2X^2)/X = (X + Y + Z)^2X$

- Respuesta: B= ( X= (( X + Y + Z )² ) X )