# RESUMEN del FUNCIONAMIENTO de los TRANSISTORES BIPOLARES y MOS en CORTE y SATURACIÓN

Los temas 2,3 y 4 no son objeto de examen, pero una pequeña parte del conocimiento del tema 2 sí que hace falta para el estudio del circuito de tiempo 555 y de las celdas de memoria. Este conocimiento sí que es imprescindible que conozcáis los informáticos. Os recomiendamos que leáis dicho tema y que os centréis en los apartados 2.6 (El transistor Bipolar en Corte y Saturación, pags. 113 a 117) y apartado 2.9 para los transistores MOS. De todas formas, el conocimiento que hace falta es muy sencillo y lo resumimos a continuación.

### 1. TRANSISTORES BIPOLARES

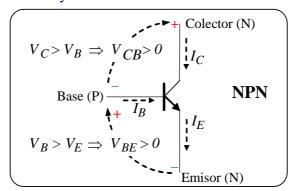

El único tipo de transistor bipolar que se usa en esta asignatura (celdas de memoria) es NPN, por tanto, su funcionamiento resumido es el que se muestra a continuación.

En la siguiente figura presentamos un transistor bipolar tipo NPN con los convenios usados para las tensiones y corriente.

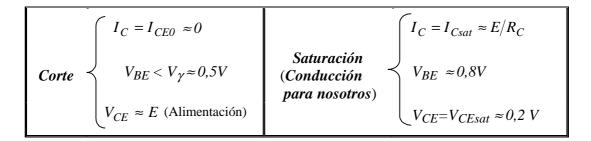

- 1.a) Si la tensión de la Base (silicio tipo P) del transistor supera a la tensión del Emisor (silicio tipo N) en el valor de la tensión de despegue de la unión P-N (VB –VE= 0,7V) el transistor conduce y entonces, entre Colector y Emisor presenta muy poca resistencia. Equivale a un cortocircuito entre esos terminales (Colector y Emisor) y deja pasar toda la corriente.

- 1.b) Si la tensión de la Base no supera en esa cantidad (0,7V) a la tensión del Emisor, entonces el transistor no conduce, está al corte y presenta muy alta impedancia entre su Colector y Emisor. Equivale a un circuito abierto entre ambos terminales.

Como podemos observar funciona como si fuera un interruptor en el que la corriente que circula entre su Colector y Emisor está controlada por la tensión existente entre Base y Emisor.

En el siguiente cuadro resumimos dicho funcionamiento.

FSD (UNED)

## 2. TRANSISTORES MOS

El funcionamiento es análogo y el conocimiento necesario se puede resumir como mostramos a continuación.

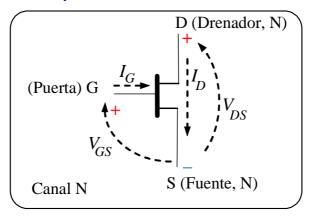

### 2.a) Transistores MOS canal N (NMOS)

En la siguiente figura presentamos un transistor MOS canal N con los convenios usados para las tensiones y corriente.

- 2.a.1) Si la tensión de la Puerta es mayor que la tensión de Fuente (V<sub>G</sub>>V<sub>S</sub>, para el análisis de las celdas podemos despreciar el valor de la tensión umbral, V<sub>T</sub>) el transistor conduce, presenta muy baja impedancia entre Drenador y Fuente y equivale a un cortocircuito entre esos dos terminales. En digital esta condición equivale a que en la puerta del transistor MOS cana N tiene un "1".

- 2.a.2) Si la tensión de la Puerta es menor que la tensión de Fuente ( $V_G < V_{S_s}$  para nuestro uso en digital equivale a que en la puerta tiene un "0") el transistor pasa al corte (no conduce), presenta muy alta impedancia entre Drenador y Fuente y equivale a un circuito abierto entre esos dos terminales.

Este funcionamiento de los transistores NMOS lo resumimos en el siguiente cuadro:

| Corte (no conduce) | $V_{GS} < 0 \Rightarrow$ "0"  | Alta Z entre Drenador y Fuente     |

|--------------------|-------------------------------|------------------------------------|

|                    |                               | Equivale a un Circuito abierto     |

| Conducción         | $V_{GS} > 0, \rightarrow$ "1" | Muy baja Z entre Drenador y Fuente |

|                    |                               | Equivale a un Cortocircuito        |

FSD (UNED)

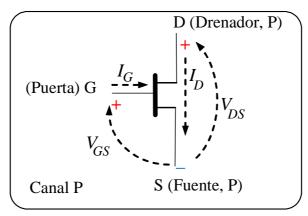

## **2.b) Transistores MOS canal P (PMOS):**

En la siguiente figura presentamos un transistor MOS canal P con los convenios usados para las tensiones y corriente.

Su funcionamiento es justo al revés que el del MOS canal N.

- 2.b.1) Si la tensión de la Puerta es menor que la tensión de Fuente (equivalente en digital a un tener en la puerta un "0") el transistor conduce, presenta muy baja impedancia entre Drenador y Fuente y equivale a un cortocircuito entre esos dos terminales.

- 2.b.2) Si la tensión de la Puerta es mayor que la tensión de Fuente (equivalente en digital a tener en la puerta un "1") el transistor pasa al corte, presenta muy alta impedancia entre Drenador y Fuente y equivale a un circuito abierto entre esos dos terminales

Este funcionamiento de los transistores PMOS lo resumimos en el siguiente cuadro:

| Corte (no conduce) | $V_{GS} > 0 \rightarrow "1"$    | Alta Z entre Drenador y Fuente     |

|--------------------|---------------------------------|------------------------------------|

|                    |                                 | Equivale a un Circuito abierto     |

| Conducción         | $V_{GS}$ < 0, $\rightarrow$ "0" | Muy baja Z entre Drenador y Fuente |

|                    |                                 | Equivale a un Cortocircuito        |

De nuevo, el funcionamiento de estos transistores es el de un interruptor en el que la corriente que circula entre su Drenador y la Fuente está controlada por la tensión de la Puerta.

\*\*\*\*\*\*\*

FSD (UNED) 3